# Smart high-side NMOS-power switch

### ITS4100S-SJ-N

### **Features**

- CMOS compatible input

- Switching all types of resistive, inductive and capacitive loads

- Fast demagnetization of inductive loads

- Very low standby current

- Optimized Electromagnetic Compatibility (EMC)

- Overload protection

- Current limitation

- · Short circuit protection

- Thermal shutdown with restart

- Overvoltage protection (including load dump)

- Reverse battery protection with external resistor

- Loss of GND and loss of Vbb protection

- Electrostatic Discharge Protection (ESD)

- Green Product (RoHS compliant)

## **Potential applications**

- All types of resistive, inductive and capacitive loads

- Power switch for 12V and 24V DC applications with CMOS compatible control interface

- Driver for electromagnetic relays

- Power management for high-side-switching with low current consumption in OFF-mode

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC.

## **Description**

The ITS4100S-SJ-N is a protected single channel Smart High-Side NMOS-Power Switch in a PG-DSO-8 package with charge pump and CMOS compatible input. The device is monolithically integrated in Smart technology.

### Table 1 Product summary

| Parameter                   | Symbol              | Values                    |

|-----------------------------|---------------------|---------------------------|

| Overvoltage protection      | $V_{SAZmin}$        | 41 V                      |

| Operating voltage range     | $V_{S}$             | 5V < V <sub>S</sub> < 34V |

| On-state resistance         | R <sub>DSON</sub>   | typ. 70 mΩ                |

| Nominal load current        | I <sub>L(nom)</sub> | 2.0 A                     |

| Operating temperature range | $T_{\rm j}$         | -40°C to 125°C            |

| Stand-by current            | I <sub>SSTB</sub>   | 15 μΑ                     |

| Туре          | Package  | Marking |

|---------------|----------|---------|

| ITS4100S-SJ-N | PG-DSO-8 | I100SN  |

## **Table of Contents**

| 1   | Block diagram and terms         | . 4 |

|-----|---------------------------------|-----|

| 2   | Pin configuration               | . 5 |

| 2.1 | Pin assignment                  |     |

| 2.2 | Pin definitions and functions   | . 5 |

| 3   | General product characteristics | . 6 |

| 3.1 | Absolute maximum ratings        |     |

| 3.2 | Functional range                | . 7 |

| 3.3 | Thermal resistance              | . 7 |

| 4   | Electrical characteristics      | . 8 |

| 5   | Typical performance graphs      | 10  |

| 6   | Application information         | 15  |

| 6.1 | Application diagram             |     |

| 6.2 | Special feature description     | 16  |

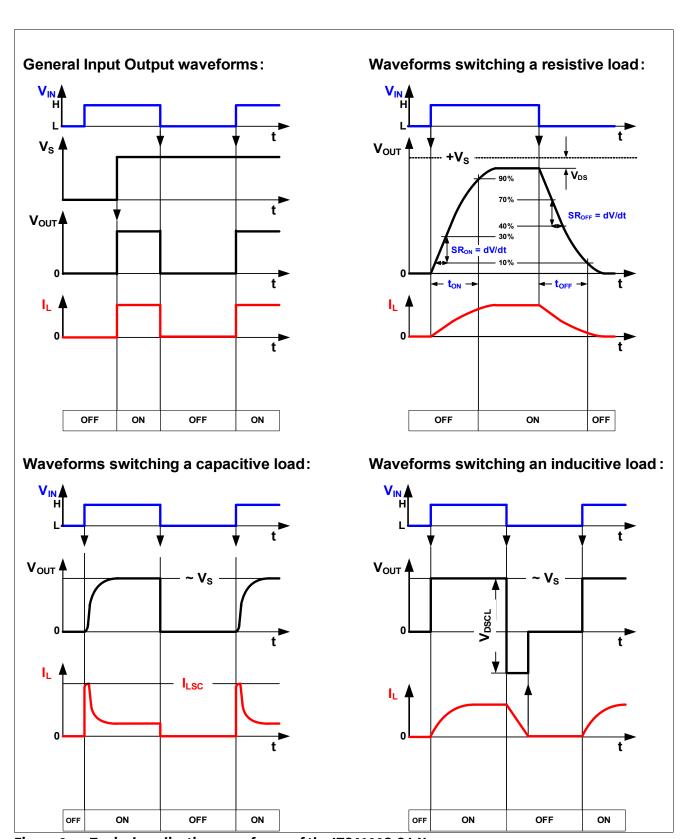

| 6.3 | Typical application waveforms   | 17  |

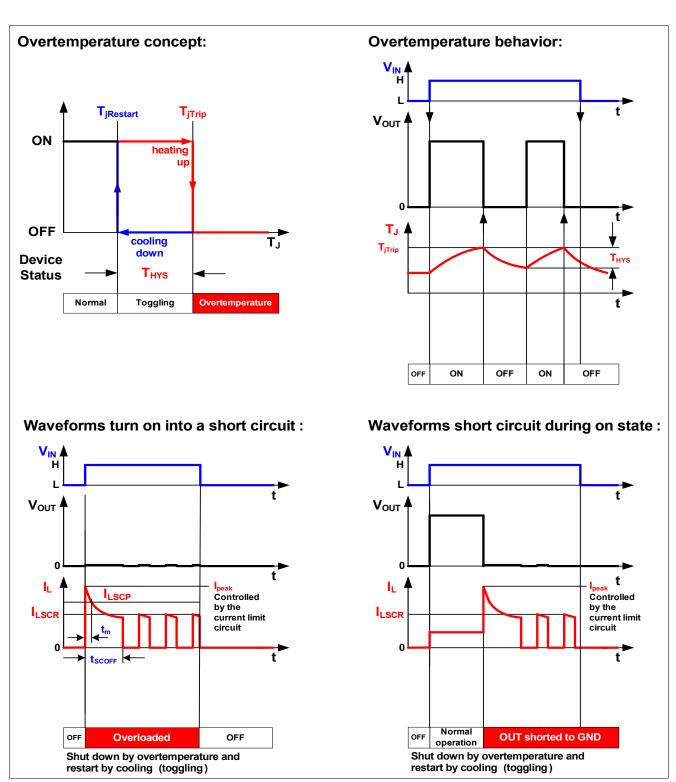

| 6.4 | Protection behavior             | 18  |

| 7   | Package information             | 19  |

| 8   | Revision history                | 20  |

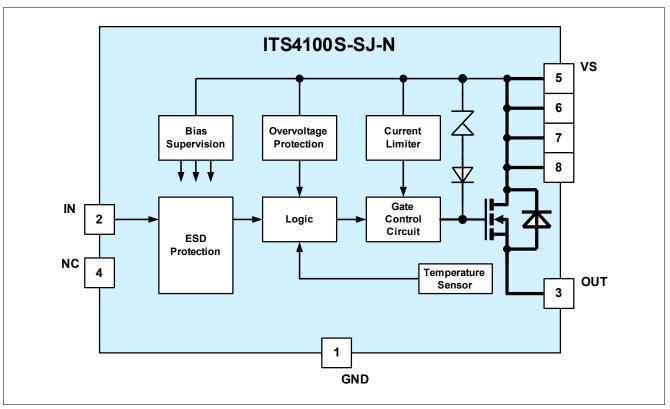

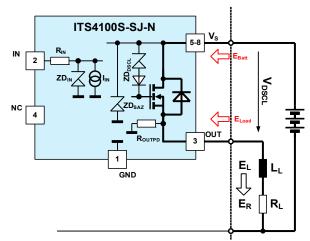

**Block diagram and terms**

## 1 Block diagram and terms

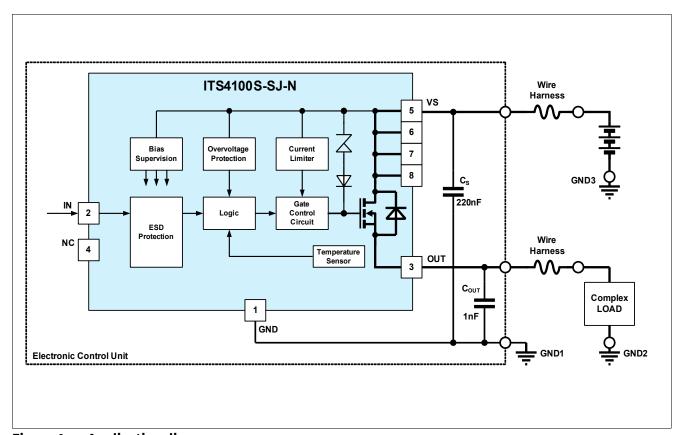

Figure 1 Block diagram

Figure 2 Terms - parameter definition

infineon

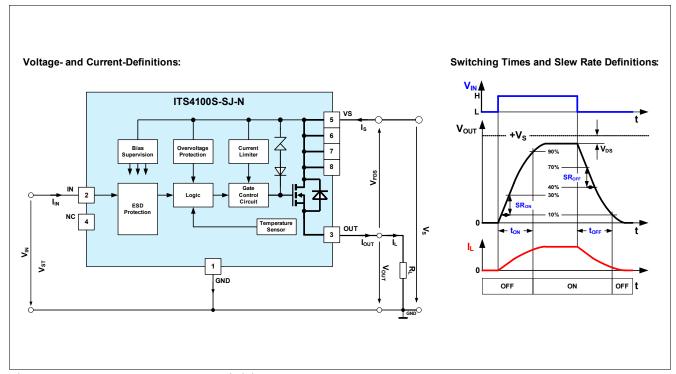

Pin configuration

# 2 Pin configuration

## 2.1 Pin assignment

Figure 3 Pin configuration top view, PG-DSO-8

### 2.2 Pin definitions and functions

| Pin        | Symbol | Function                                                                                                     |

|------------|--------|--------------------------------------------------------------------------------------------------------------|

| 1          | GND    | Logic ground                                                                                                 |

| 2          | IN     | Input, controls the power switch; the powerswitch is ON when high                                            |

| 3          | OUT    | Output to the load                                                                                           |

| 4          | NC     | Not connected                                                                                                |

| 5, 6, 7, 8 | VS     | Supply voltage (design the wiring for the maximum short circuit current and also for low thermal resistance) |

# infineon

**General product characteristics**

### **3** General product characteristics

### 3.1 Absolute maximum ratings

Table 2 Absolute maximum ratings  $^{1)}$  at  $T_{j}$  = 25°C unless otherwise specified. Currents flowing into the device unless otherwise specified in chapter "Block Diagram and Terms"

| Parameter                                                              | Symbol           |      | Value | es              | Unit | Note or                        | Number                                       |

|------------------------------------------------------------------------|------------------|------|-------|-----------------|------|--------------------------------|----------------------------------------------|

|                                                                        |                  | Min. | Тур.  | Max.            |      | <b>Test Condition</b>          |                                              |

| Supply voltage VS                                                      |                  |      |       |                 |      |                                | 11                                           |

| Voltage                                                                | $V_{S}$          | -    | -     | 40              | V    | _                              | 4.1.1                                        |

| Voltage for short circuit protection                                   | $V_{\rm SSC}$    | -    | -     | V <sub>s</sub>  | V    | -40°C < T <sub>j</sub> < 150°C | 4.1.2                                        |

| Output stage OUT                                                       |                  |      |       |                 |      |                                |                                              |

| Output current; (short circuit current see electrical characteristics) | I <sub>OUT</sub> | _    | _     | self<br>limited | А    | -                              | 4.1.3                                        |

| Input IN                                                               |                  |      |       |                 |      |                                | 11                                           |

| Voltage                                                                | $V_{IN}$         | -10  | _     | 16              | V    | _                              | 4.1.4                                        |

| Current                                                                | I <sub>IN</sub>  | -5   | _     | 5               | mA   | _                              | 4.1.5                                        |

| Temperatures                                                           |                  |      |       |                 |      |                                | <u>.                                    </u> |

| Junction temperature                                                   | T <sub>j</sub>   | -40  | _     | 125             | °C   | _                              | 4.1.6                                        |

| Storage temperature                                                    | $T_{\rm stg}$    | -55  | _     | 125             | °C   | _                              | 4.1.7                                        |

| Power dissipation                                                      |                  |      |       |                 |      |                                |                                              |

| Ta = 25 °C <sup>2)</sup>                                               | P <sub>tot</sub> | _    | _     | 1.5             | W    | _                              | 4.1.8                                        |

| Inductive load switch-off energy dis                                   |                  |      |       |                 |      |                                |                                              |

| Tj = 125 °C; $V_S$ =13.5V; IL= 1.0A <sup>3)</sup>                      | E <sub>AS</sub>  | _    | _     | 870             | mJ   | single pulse                   | 4.1.9                                        |

| ESD susceptibility                                                     |                  |      |       |                 |      |                                |                                              |

| ESD susceptibility (input pin IN)                                      |                  | -1   | _     | 1               | kV   | HBM <sup>4)</sup>              | 4.1.10                                       |

| ESD susceptibility (output pin OUT)                                    | $V_{ESD}$        | -6   | _     | 6               | kV   | HBM <sup>4)</sup>              | 4.1.12                                       |

| ESD susceptibility (all other pins)                                    | $V_{ESD}$        | -4   | -     | 4               | kV   | HBM <sup>4)</sup>              | 4.1.11                                       |

<sup>1)</sup> Not subject to production test, specified by design

Note:

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" the normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

<sup>2)</sup> Device on 50mm\*50mm\*1.5mm epoxy PCB FR4 with 6 cm2 (one layer, 70mm thick) copper area for Vbb connection. PCB is vertical without blown air

<sup>3)</sup> Not subject to production test, specified by design

<sup>4)</sup> ESD susceptibility HBM according to ANSI/ESDA/JEDEC JS001 (1.5 kΩ, 100 pF)

### **General product characteristics**

### 3.2 Functional range

Table 3 Functional range

| Parameter                 | Symbol         |      | Values |      | Unit | Note or                   | Number |  |

|---------------------------|----------------|------|--------|------|------|---------------------------|--------|--|

|                           |                | Min. | Тур.   | Max. |      | <b>Test Condition</b>     |        |  |

| Nominal operating voltage | V <sub>S</sub> | 5    | -      | 34   | ٧    | V <sub>S</sub> increasing | 4.2.1  |  |

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### 3.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

Table 4 Thermal resistance<sup>1)</sup>

| Parameter                                                           | Symbol                       |      | Values | ;    | Unit | Note or               | Number |

|---------------------------------------------------------------------|------------------------------|------|--------|------|------|-----------------------|--------|

|                                                                     |                              | Min. | Тур.   | Max. |      | <b>Test Condition</b> |        |

| Thermal resistance - junction to pin5                               | R <sub>thj-pin5</sub>        | _    | 32.0   | _    | K/W  | -                     | 4.3.1  |

| Thermal resistance - junction to ambient - 1s0p, minimal footprint  | R <sub>thJA_1s0p</sub>       | _    | 135.3  | -    | K/W  | 2)                    | 4.3.2  |

| Thermal resistance - junction to ambient - 1s0p, 300mm <sup>2</sup> | R <sub>thJA_1s0p_300mm</sub> | _    | 86.1   | -    | K/W  | 3)                    | 4.3.3  |

| Thermal resistance - junction to ambient - 1s0p, 600mm <sup>2</sup> | R <sub>thJA_1s0p_600mm</sub> | _    | 75.3   | _    | K/W  | 4)                    | 4.3.4  |

| Thermal resistance - junction to ambient - 2s2p                     | R <sub>thJA_2s2p</sub>       | _    | 66.8   | _    | K/W  | 5)                    | 4.3.5  |

| Thermal resistance - junction to ambient with thermal vias - 2s2p   | R <sub>thJA_2s2p</sub>       | _    | 58.4   | _    | K/W  | 6)                    | 4.3.6  |

<sup>1)</sup> Not subject to production test, specified by design

- 2) Specified  $R_{thJA}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, footprint; the product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 3) Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, Cu, 300mm<sup>2</sup>; the product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 4) Specified  $R_{thJA}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, 600mm<sup>2</sup>; the product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 5) Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu).

- 6) Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board with two thermal vias; the product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu. The diameter of the two vias are equal 0.3mm and have a plating of 25 $\mu$ m with a copper heatsink area of 3mm x 2mm). JEDEC51-7: The two plated-through hole vias should have a solder land of no less than 1.25 mm diameter with a drill hole of no less than 0.85 mm diameter.

# **(infineon**

### **Electrical characteristics**

### 4 Electrical characteristics

Table 5  $V_s$ =13.5V;  $T_j$ = -40°C to 125°C; all voltages with respect to ground. Currents flowing into the device unless otherwise specified in chapter "Block diagram and terms". Typical values at  $V_s$ =13.5V,  $T_i$ =25°C

| Parameter                                                                                                       | Symbol             |         | Value    | S    | Unit   | Note or                                                                                 | Number |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------|---------|----------|------|--------|-----------------------------------------------------------------------------------------|--------|--|

|                                                                                                                 |                    | Min.    | Тур.     | Max. |        | <b>Test Condition</b>                                                                   |        |  |

| Powerstage                                                                                                      |                    |         | •        |      |        |                                                                                         |        |  |

| NMOS ON resistance                                                                                              | $R_{DSON}$         | _       | 70       | 100  | mΩ     | $I_{OUT}$ = 2A; $T_j$ = 25°C;<br>9V < $V_S$ < 34V;<br>$V_{IN}$ = 5V                     | 5.0.1  |  |

| NMOS ON resistance                                                                                              | $R_{DSON}$         | _       | 140      | 200  | mΩ     | $I_{OUT}$ = 2A; $T_j$ = 125°C;<br>9V < $V_S$ < 34V;<br>$V_{IN}$ = 5V                    | 5.0.2  |  |

| Nominal load current;<br>device on PCB <sup>1)</sup>                                                            | I <sub>LNOM</sub>  | 2.0     | 2.4      | -    | А      | T <sub>pin5</sub> = 85°C                                                                | 5.0.3  |  |

| Timings of power stages <sup>2)</sup>                                                                           | 1                  | 1       |          | "    | 1      |                                                                                         |        |  |

| Turn ON time (to 90% of $V_{out}$ );<br>L to H transition of $V_{IN}$                                           | t <sub>ON</sub>    | _       | 90       | 170  | μs     | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                           | 5.0.4  |  |

| Turn OFF time (to 10% of $V_{\text{out}}$ );<br>H to L transition of $V_{\text{IN}}$                            | t <sub>OFF</sub>   | -       | 90       | 230  | μs     | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                           | 5.0.5  |  |

| ON-slew rate; $\Delta V_{\rm OUT}/\Delta t$ ; (10 to 30% of $V_{\rm out}$ ); L to H transition of $V_{\rm IN}$  | SR <sub>ON</sub>   | -       | 0.8      | 1.7  | V/μs   | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                           | 5.0.6  |  |

| OFF-slew rate; $\Delta V_{\rm OUT}/\Delta t$ ; (70 to 40% of $V_{\rm out}$ ); H to L transition of $V_{\rm IN}$ | SR <sub>OFF</sub>  | _       | 0.8      | 1.7  | V / μs | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                           | 5.0.7  |  |

| Under voltage lockout (charge                                                                                   | pump start         | -stop-ı | restart) |      |        |                                                                                         | -      |  |

| Supply undervoltage;<br>charge pump stop voltage                                                                | V <sub>SUV</sub>   | _       | _        | 5.5  | V      | $V_{\rm S}$ decreasing                                                                  | 5.0.8  |  |

| Supply startup voltage;<br>Charge pump restart voltage                                                          | V <sub>SSU</sub>   | -       | 4.0      | 5.5  | V      | $V_{\rm S}$ increasing                                                                  | 5.0.9  |  |

| Current consumption                                                                                             | -                  |         |          |      |        |                                                                                         | -      |  |

| Operating current                                                                                               | $I_{GND}$          | _       | 0.5      | 1.3  | mA     | V <sub>IN</sub> = 5V                                                                    | 5.0.10 |  |

| Standby current                                                                                                 | I <sub>SSTB</sub>  | -       | -        | 10   | μΑ     | $V_{IN} = 0V; V_{OUT} = 0V$<br>-40°C < $T_i$ < 85°C                                     | 5.0.11 |  |

| Standby current                                                                                                 | I <sub>SSTB</sub>  | _       | _        | 15   | μΑ     | $V_{IN} = 0V; V_{OUT} = 0V$<br>$T_{i} = 125^{\circ}C$                                   | 5.0.12 |  |

| Output leakage current                                                                                          | I <sub>OUTLK</sub> | _       | _        | 5    | μΑ     | $V_{\rm IN} = 0V; V_{\rm OUT} = 0V$                                                     | 5.0.13 |  |

| Protection functions 3)                                                                                         | 1                  | 1       |          |      |        |                                                                                         |        |  |

| Initial peak short circuit current limit                                                                        | I <sub>LSCP</sub>  | _       | _        | 18   | А      | $T_{\rm j}$ = -40°C; $V_{\rm S}$ = 20V<br>$V_{\rm IN}$ = 5.0V; $t_{\rm m}$ =150 $\mu$ s | 5.0.14 |  |

#### **Electrical characteristics**

$V_s$ =13.5V;  $T_i$  = -40°C to 125°C; all voltages with respect to ground. Currents flowing into the Table 5 device unless otherwise specified in chapter "Block diagram and terms". Typical values at  $V_s = 13.5V, T_i = 25^{\circ}C$

| Parameter                                                                                     | Symbol             |      | Value | s    | Unit | Note or                                                                                | Number |  |

|-----------------------------------------------------------------------------------------------|--------------------|------|-------|------|------|----------------------------------------------------------------------------------------|--------|--|

|                                                                                               |                    | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                  |        |  |

| Initial peak short circuit current limit                                                      | I <sub>LSCP</sub>  | -    | 10    | -    | A    | $T_{\rm j}$ = 25°C; $V_{\rm S}$ = 20V<br>$V_{\rm IN}$ = 5.0V; $t_{\rm m}$ =150 $\mu$ s | 5.0.15 |  |

| Initial peak short circuit current limit                                                      | I <sub>LSCP</sub>  | 4    | -     | -    | А    | $T_{\rm j}$ =125°C; $V_{\rm S}$ = 20V<br>$V_{\rm IN}$ = 5.0V; $t_{\rm m}$ =150 $\mu$ s | 5.0.16 |  |

| Repetitive short circuit current limit $T_j = T_{jTrip}$ ; see timing diagrams                | I <sub>LSCR</sub>  | _    | 7     | -    | А    | V <sub>IN</sub> = 5.0V                                                                 | 5.0.17 |  |

| Output clamp at $V_{\text{OUT}} = V_{\text{S}} - V_{\text{DSCL}}$ (inductive load switch off) | $V_{ m DSCL}$      | 41   | 47    | -    | V    | I <sub>S</sub> = 4 mA                                                                  | 5.0.18 |  |

| Overvoltage protection $V_{\text{OUT}} = V_{\text{S}} - V_{\text{ONCL}}$                      | V <sub>SAZ</sub>   | 41   | -     | -    | V    | I <sub>S</sub> = 4 mA                                                                  | 5.0.19 |  |

| Thermal overload<br>trip temperature                                                          | $T_{\rm jTrip}$    | 150  | -     | -    | °C   | -                                                                                      | 5.0.20 |  |

| Thermal hysteresis                                                                            | $T_{HYS}$          | -    | 10    | -    | K    | _                                                                                      | 5.0.21 |  |

| Reverse battery <sup>4)</sup>                                                                 |                    |      |       |      |      |                                                                                        |        |  |

| Continuous reverse battery voltage                                                            | $V_{SREV}$         | - 32 | -     | -    | V    | -                                                                                      | 5.0.22 |  |

| Forward voltage of the drain-<br>source reverse diode                                         | V <sub>FDS</sub>   | _    | 600   | -    | mV   | $I_{FDS} = 200 \text{ mA};$<br>$V_{IN} = 0V; T_j = 125^{\circ}C$                       | 5.0.23 |  |

| Input interface; pin IN                                                                       | II.                | 1    | II.   | l'   | "    |                                                                                        |        |  |

| Input turn-ON voltage<br>(logic input high level)                                             | V <sub>INON</sub>  | 2.2  | -     | -    | V    | -                                                                                      | 5.0.24 |  |

| Input turn-OFF voltage (logic input low-level)                                                | V <sub>INOFF</sub> | -    | -     | 0.8  | V    | -                                                                                      | 5.0.25 |  |

| Input threshold hysteresis                                                                    | $V_{INHYS}$        | _    | 0.3   | _    | ٧    | -                                                                                      | 5.0.26 |  |

| Off state input current                                                                       | I <sub>INOFF</sub> | 1    | _     | 30   | μΑ   | $V_{IN} = 0.7V$                                                                        | 5.0.27 |  |

| On state input current                                                                        | I <sub>INON</sub>  | 1    | _     | 30   | μΑ   | V <sub>IN</sub> = 5.0V                                                                 | 5.0.28 |  |

| Input resistance                                                                              | R <sub>IN</sub>    | 1.5  | 3.5   | 5.0  | kΩ   | _                                                                                      | 5.0.29 |  |

- 1) Device on 50mm x 50mm x 1,5mm epoxy FR4 PCB with 6cm<sup>2</sup> (one layer copper 70um thick) copper area for supply voltage connection. PCB in vertical position without blown air.

- 2) Timing values only with high slewrate input signal; otherwise slower.

- 3) Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

- 4) Requires a 150  $\Omega$  resistor in GND connection. The reverse load current trough the intrinsic drain-source diode of the power-MOS has to be limited by the connected load. Power dissipation is higher compared to normal operation due to the voltage drop across the drain-source diode. The temperature protection is not functional during reverse current operation! Input current has to be limited (see max ratings).

### ITS4100S-SJ-N

**Typical performance graphs**

#### **Typical performance graphs** 5

### **Typical performance characteristics**

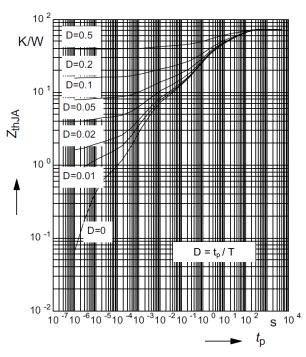

### Transient thermal impedance $\mathbf{Z}_{\text{thJA}}$ versus pulse time t<sub>p</sub> @ 6cm<sup>2</sup> heatsink area

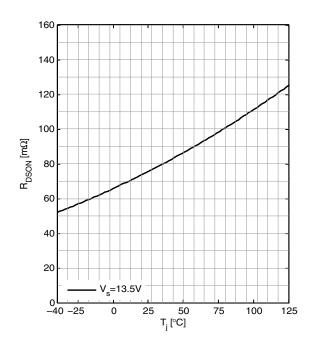

### On-resistance $R_{DSON}$ versus junction temperature Ti

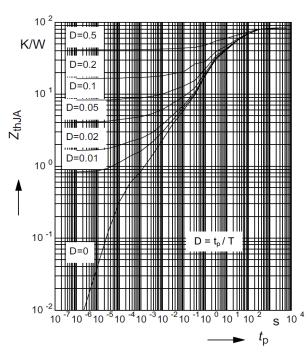

### Transient thermal impedance $Z_{thJA}$ versus pulse time $t_p$ @ minimum footprint

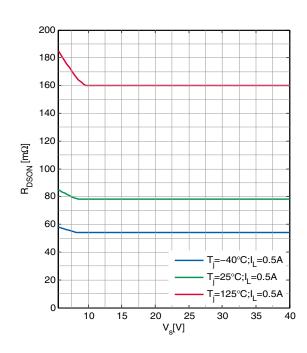

### On-resistance R<sub>DSON</sub> versus supply voltage Vs

# **Smart high-side NMOS-power switch**

# ITS4100S-SJ-N

# **(**infineon

### **Typical performance graphs**

### **Typical performance characteristics**

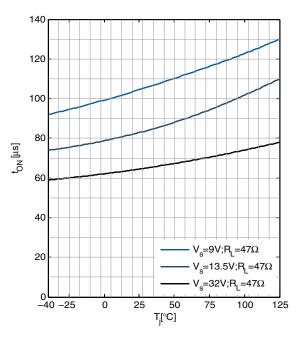

### Switch ON time $t_{\rm ON}$ versus junction temperature $T_i$

### ON slewrate SR<sub>ON</sub> versus junction temperature $T_i$

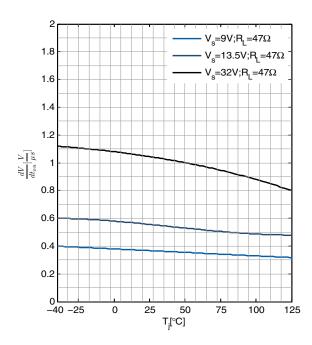

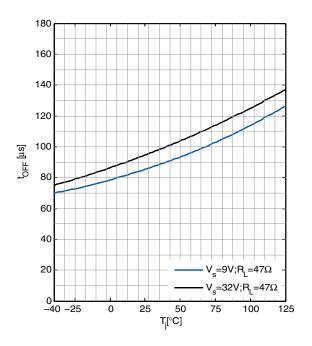

### Switch OFF time $t_{\rm OFF}$ versus junction temperature $T_i$

### **OFF slewrate** *SR***OFF versus** junction temperature $T_i$

### **Typical performance graphs**

### **Typical performance characteristics**

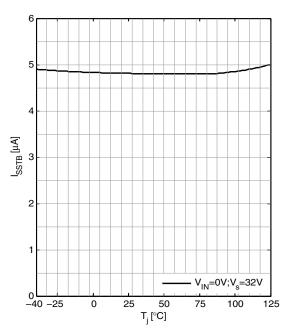

# Standby current $I_{\text{SSTB}}$ versus junction temperature $T_{\text{i}}$

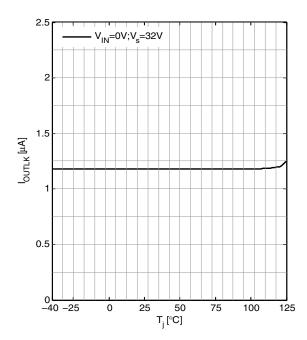

# Output leakage current $I_{\text{OUTLK}}$ versus junction temperature $T_{\text{j}}$

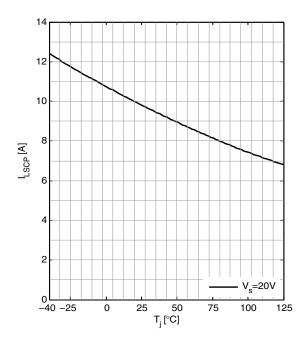

# Initial peak short circuit current limit $I_{LSCP}$ versus junction temperature $T_i$

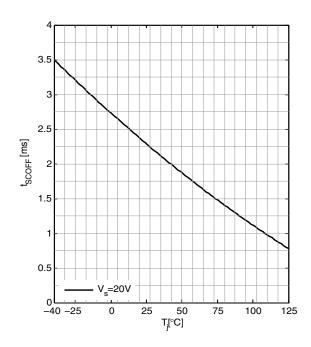

# Initial short circuit shutdown time $t_{\text{SCOFF}}$ versus junction temperature $T_{\text{i}}$

# **Smart high-side NMOS-power switch**

### ITS4100S-SJ-N

### **Typical performance graphs**

### **Typical performance characteristics**

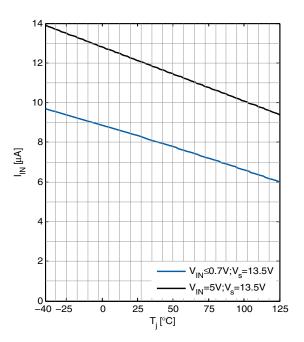

### Input current consumption $I_{IN}$ versus junction temperature $T_i$

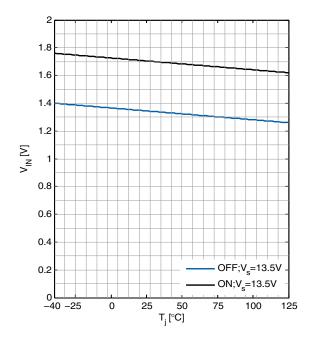

### Input threshold voltage $V_{\mathrm{INH,L}}$ versus junction temperature $T_{\rm j}$

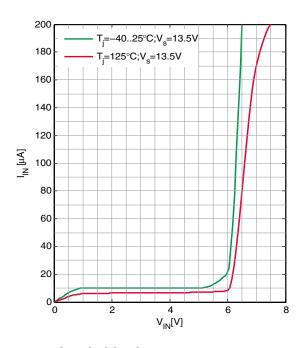

### Input current consumption $I_{IN}$ versus input voltage V<sub>IN</sub>

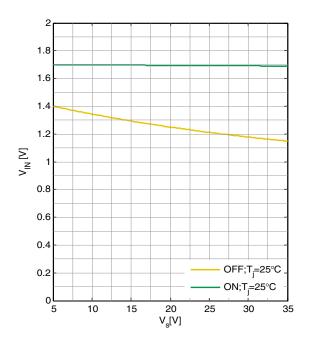

Input threshold voltage  $V_{\text{INH,L}}$  versus supply voltage V<sub>S</sub>

### **Typical performance graphs**

### **Typical performance characteristics**

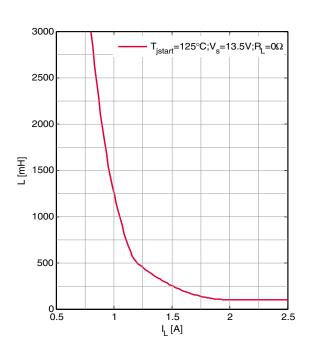

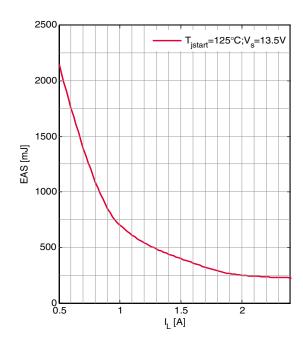

# Max. allowable load inductance L versus load current $I_L$

# Max. allowable inductive single pulse switch-off energy $E_{\rm AS}$ versus load current $I_{\rm L}$

# ITS4100S-SJ-N

### **Application information**

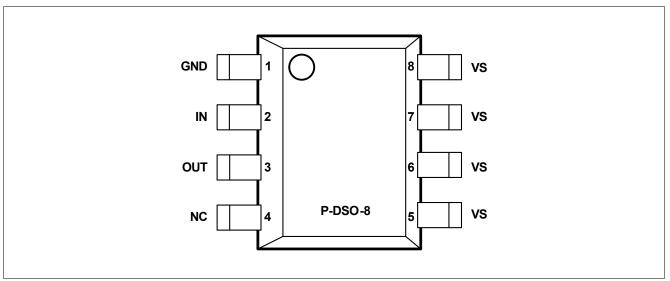

#### **Application information** 6

#### **Application diagram** 6.1

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty for a certain functionality, condition or quality of the device.

Figure 4 Application diagram

The ITS4100S-SJ-N can be connected directly to a supply network. It is recommended to place a ceramic capacitor (e.g. C<sub>s</sub> = 220nF) between supply and GND to avoid line disturbances. Wire harness inductors/resistors are sketched in the application circuit above.

The complex load (resistive, capacitive or inductive) must be connected to the output pin OUT.

A built-in current limit protects the device against destruction.

The ITS4100S-SJ-N can be switched on and off with standard logic ground related logic signal at pin IN.

In standby mode (IN=L) the ITS4100S-SJ-N is deactivated with very low current consumption.

The output voltage slope is controlled during on and off transition to minimize emissions. Only a small ceramic capacitor COUT=1nF is recommended to attenuate RF noise.

In the following chapters the main features, some typical waveforms and the protection behavior of the ITS4100S-SJ-N is shown. For further details please refer to application notes on the Infineon homepage.

### **Application information**

Supply over voltage:

#### **Special feature description** 6.2

# ITS4100S-SJ-N GND ZL RGNE

If over-voltage is applied to the V<sub>S</sub>-Pin:

Voltage is limited to V<sub>ZDSAZ</sub>; current can be calculated:

$I_{ZDSAZ} = (V_S - V_{ZDSAZ}) / R_{GND}$

A typical value for RGND is  $150\Omega$ .

In case of ESD pulse on the input pin there is in both polarities a peak current  $I_{INpeak} \sim V_{ESD}$  /  $R_{IN}$

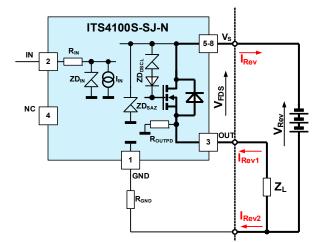

#### Supply reverse voltage:

If reverse voltage is applied to the device:

1.) Current via load resistance RL:

$I_{Rev1} = (V_{Rev} - V_{FDS}) / R_L$

2.) Current via Input pin IN and dignostic pin ST:

$I_{Rev2} = I_{ST} + I_{IN} \sim (V_{Rev} - V_{CC})/R_{IN} + (V_{Rev} - V_{CC})/R_{ST1,2}$ Current I<sub>ST</sub> must be limited with the extrernal series resistor R<sub>STS</sub>. Both currents will sum up to:

$$I_{Rev} = I_{Rev1} + I_{Rev2}$$

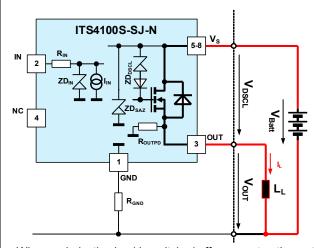

#### Drain-Source power stage clamper VDSCL:

When an inductive load is switched off a current path must be established until the current is sloped down to zero (all energy removed from the inductive load ). For that purpose the series combination Z<sub>DSCL</sub> is connected between Gate and Drain of the power DMOS acting as an active clamp.

When the device is switched off, the voltage at OUT turns negative until V<sub>DSCL</sub> is reached.

The voltage on the inductive load is the difference between  $V_{DSCL}$  and  $V_{S}$ .

### **Energy calculation:**

Energy stored in the load inductance is given by:  $E_1 = I_1^2 L/2$

While demagnetizing the load inductance the energy dissipated by the Power-DMOS is:

$$E_{AS} = E_S + E_L - E_R$$

With an approximate solution for  $R_L = 0\Omega$ :

$$E_{AS} = \frac{1}{2} * L * I_{L}^{2} * \{(1 - V_{S} / (V_{S} - V_{DSCL}))\}$$

Figure 5 **Special feature description**

**Application information**

#### **Typical application waveforms** 6.3

Figure 6 Typical application waveforms of the ITS4100S-SJ-N

**Application information**

#### **Protection behavior** 6.4

Protective behavior of the ITS4100S-SJ-N Figure 7

# ITS4100S-SJ-N

### **Package information**

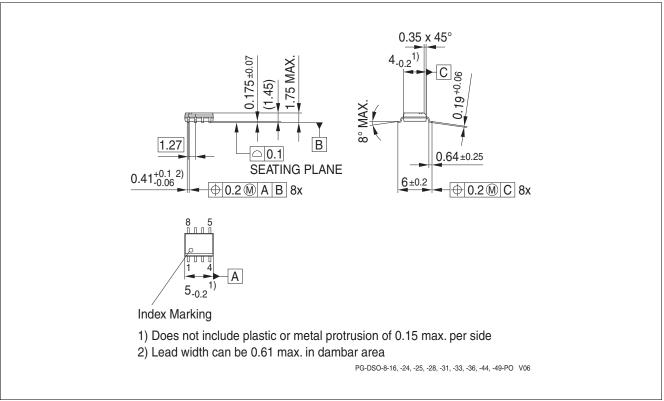

#### **Package information** 7

Figure 8 PG-DSO-8<sup>1)</sup>

### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

### **Further information on packages**

https://www.infineon.com/packages

# **Smart high-side NMOS-power switch**

ITS4100S-SJ-N

**Revision history**

#### **Revision history** 8

| Revision | Date       | Changes                                                                                                  |

|----------|------------|----------------------------------------------------------------------------------------------------------|

| 1.1      | 2019-07-25 | Datasheet updated: - ESD ratings for HBM updated according to ANSI/ESDA/JEDEC JS-001 - Editorial changes |

| 1.0      | 12-09-01   | Datasheet release                                                                                        |

#### Trademarks

Edition 2019-07-25 Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com Z8F51106905

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.